業(yè)務(wù)咨詢,可撥打15521163312�,或電郵至wenye@mooreda.com.com,或掃描文末微信二維碼與我們聯(lián)系!

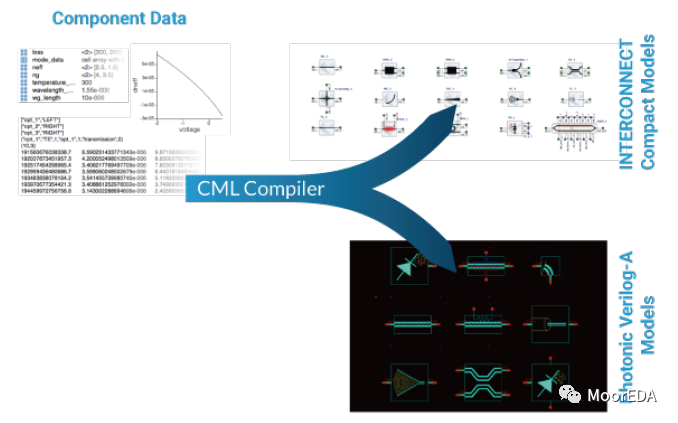

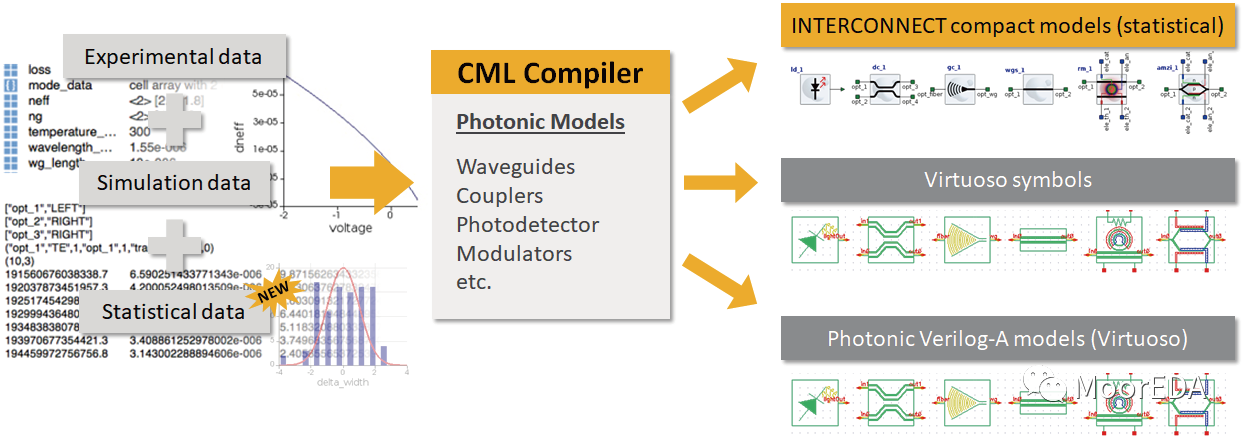

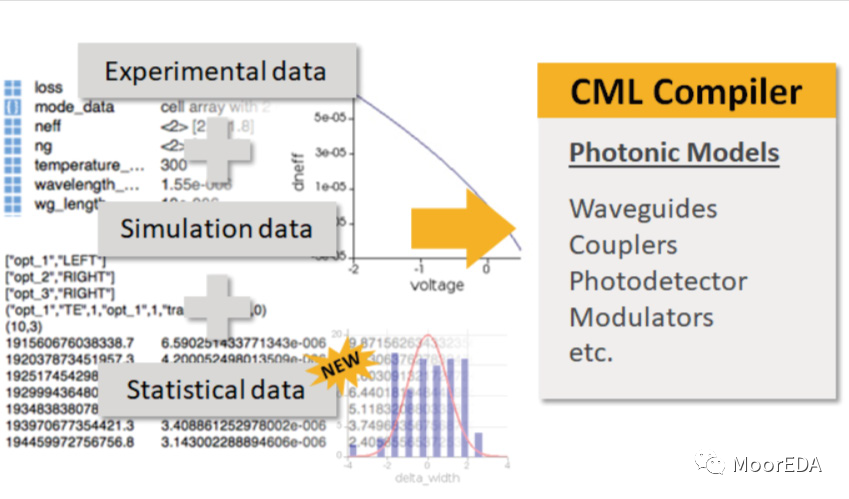

使用經(jīng)驗(yàn)證可靠的Lumerical CML Compiler能高效�、自動(dòng)化地創(chuàng)建緊湊模型庫(kù)(CML)。該工具可使用從實(shí)驗(yàn)量測(cè)或三維仿真得到的同數(shù)據(jù)源使INTERCONNECT與Verilog-A緊湊模型的創(chuàng)建�、維護(hù)�、以及QA測(cè)試全自動(dòng)化�。

▌規(guī)格概要

●?根據(jù)版本控制的CML

●?搭配范本與數(shù)據(jù)驗(yàn)證的結(jié)構(gòu)化輸入

●?測(cè)試臺(tái)自動(dòng)化生成

●?支持同數(shù)據(jù)源的輸入

●?固定或參數(shù)化的模型

●?支持統(tǒng)計(jì)分析功能

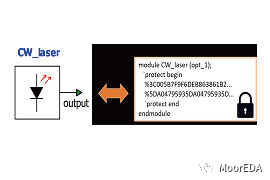

●?支持CML加密

●?Verilog-A交互仿真工具

▌主要特點(diǎn)

自動(dòng)化創(chuàng)建緊湊模型

用戶可以專注于器件設(shè)計(jì)與量測(cè),其它的工作交給CML Compiler ���。CML Compiler可以控制CML的版本��,使CML的產(chǎn)生過(guò)程自動(dòng)化并有可重復(fù)性��??勺詣?dòng)化地產(chǎn)生測(cè)試臺(tái)�,這有助于進(jìn)一步提升產(chǎn)能。

使用統(tǒng)計(jì)分析

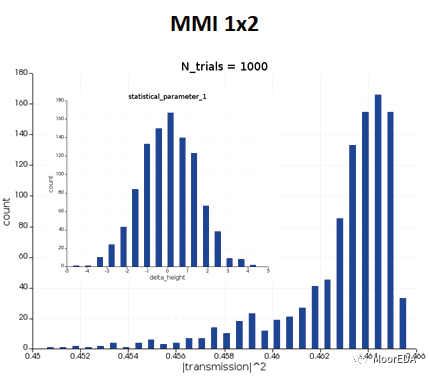

產(chǎn)生包含統(tǒng)計(jì)模型的緊湊模型庫(kù)�,并導(dǎo)入INTERCONNECT與Virtuoso來(lái)進(jìn)行蒙特卡羅與角分析。

IP保護(hù)與Verilog-A模型

從同據(jù)來(lái)源產(chǎn)生Verilog-A與INTERECONNECT光子線路模型。當(dāng)缺少或者無(wú)法獲得量測(cè)數(shù)據(jù)時(shí),可使用Ansys Lumerical業(yè)界***的3D器件仿真工具獲取并補(bǔ)充數(shù)據(jù)�����?�?僧a(chǎn)生固定以及參數(shù)化的器件��,并在豐富的現(xiàn)成模型組添加您的自定模型���。用戶可以對(duì)CML Compiler產(chǎn)生的模型使用IP加密選項(xiàng)���。